# EE105 – Fall 2015 Microelectronic Devices and Circuits Multi-Stage Amplifiers

Prof. Ming C. Wu

wu@eecs.berkeley.edu

511 Sutardja Dai Hall (SDH)

# **Example of Multi-Stage Amplifier**

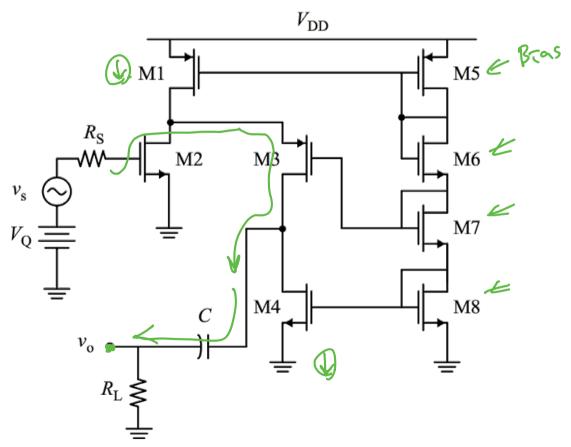

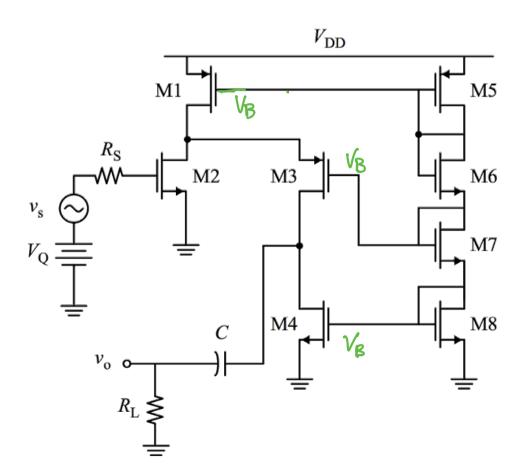

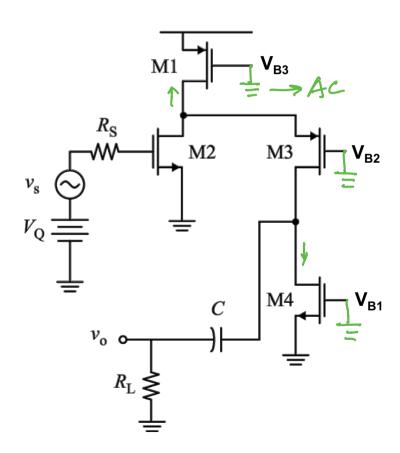

## **Cutting Through the Complexity**

- 1. Identify the "signal path" between the input and output

- 2. Eliminate "background" transistors to reduce clutter

- 3. For "background transistors, understand their role (e.g. DC biasing)

- 4. For frequency response, identify "hi-Z" nodes.

### **Eliminate Clutter**

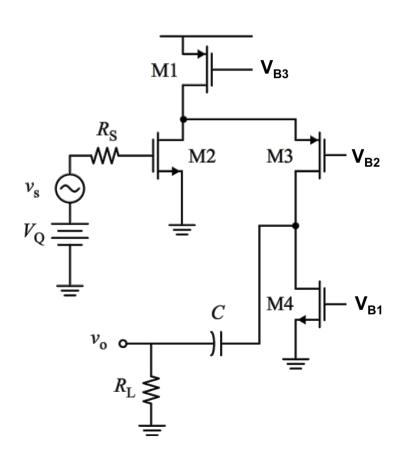

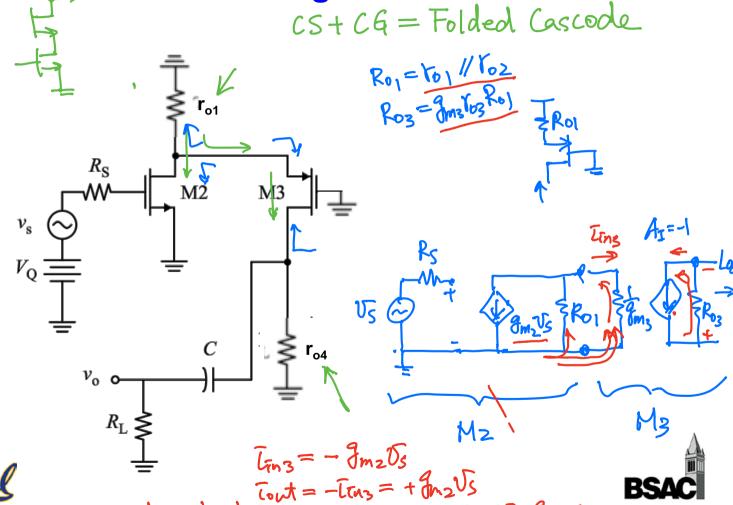

# **Identify Signal Path & Amplifier Stages**

# **DC** Biasing

# **Small-Signal Models**

Without Load: Vout = - Tout Roz = gmz Vs - gmz Voz · (Voi// Voz)

### **Two-Port Model**

#### **External Loads**

- Many applications must drive external loads that are very low impedance compared to on-chip levels

- These stages must drive high voltages/currents so linearity is a concert. We must consider "large signal" behavior

- Example: Speaker at 8 ohms versus Megaohms on-chip ...

- Follower is natural choice, but it can only "source" current (think in terms of large signals)

## **Design Issue: DC Coupling**

- Constraint: large inductors and capacitors are not available

- Output of one stage is directly connected to the input of the next stage → must consider DC levels ... why?